06/07 July 2007 B53585

Information & Know-how for Embedded Engineers

The Complementary Magazine to

www.Embedded-Control-Europe.com

### **COVER STORY:**

Flexible migration with complimentary 8-bit and 32-bit microcontrollers

# Complete solution for Remote Access Control

### Less is More

Geoff Gibson, Managing Director Express Logic UK: "...simpler solutions for less demanding applications."

With much fanfare, and justifiably so, embedded Linux has captured the spotlight in embedded software these days. Linux has earned strong interest and adoption from those in the embedded software development community looking for cost-effective operating system support for their latest embedded device. While Linux offers attractive capabilities, it also is extremely complex, making it relatively difficult to learn and use. But what if low-cost development isn't the goal? What if fast time-tomarket demands a much simpler approach? And what if available memory is limited by footprint, cost or power consumption concerns?

In those cases, a multi-megabyte Linux image just doesn't cut it. What's needed is a much smaller, much simpler solution, one that still meets the needs of the project, but doesn't dump additional baggage and complexity on top. This is one of the newer trends in embedded software – simpler solutions for less demanding applications. Consider the development time spent learning which dozen or so of the hundreds of Linux services are needed. Most embedded applications have basic needs, and only use a small subset of the comprehensive capabilities of Linux, maybe just a dozen or two services in all.

Addressing just these basic needs will enable a simple RTOS to satisfy a large number of applications in consumer electronics, medical devices, industrial automation, and wireless networking. Developers of those devices can shortcut development time by choosing an RTOS that addresses their basic needs without excess complexity. And, shortcuts in development time provide dividends in lower development costs, time to market and market share.

The adage "less is more" is supported by findings in a recent survey of embedded developers by Embedded Market Forecasters. The survey reveals that developers using certain RTOSes are more likely to complete their projects on time or even ahead of schedule than users of other operating systems.

Several small, simple RTOS products are available commercially, and most offer full source code, royalty-free licensing, commercial support. These offerings are far simpler and easier to use than Linux. The survey indicates that choosing an RTOS like this, so long as it meets your development needs, is more likely to boost your time-to-market speed over a more complex RTOS selection.

The "less is more" trend will continue, driving other developers away from the Linux solution—not because Linux is not a great technology and ideal for many applications, but because Linux just cannot handle many hard real-time, small footprint, low-cost requirements. These requirements are more and more common, and more suited to one of the small RTOSes on the market.

For fast time to market, truly, less is more.

### Low Cost 16-Bit Microcontroller

- based on the fast and low power M16C-Core from Renesas

- adding more performance to your 8-bit application

- extended fail-save functions improving system reliability

- On-chip Oszillator up to 40 MHz

- On-chip Data Flash

| Family | FLASH                   | RAM                        | Data<br>FLASH | Features                                                                                                                                                     | Package           |

|--------|-------------------------|----------------------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| R8C1B  | 4K<br>8K<br>12K<br>16K  | 384B<br>512B<br>768B<br>1K | 2K            | 1 x 16-bit timer,<br>2 x 8-bit timer,<br>1 x USART, 1 x UART,<br>1 x SSI / I <sup>2</sup> C,<br>4 x 10-bit ADC,<br>13 I/O + 3 Input                          | SSOP-20<br>QFN-28 |

| R8C27  | 8K<br>16K<br>24K<br>32K | 512B<br>1K<br>1.5K<br>1.5K | 2K            | 1 x 16-bit timer,<br>2 x 8-bit timer, RTC,<br>1 x USART, 1 UART,<br>1 x SSI / I <sup>2</sup> C, 1 x LIN,<br>12 x 10-bit ADC,<br>25 I/O + 3 Input             | LQFP-32           |

| R8C23  | 32K<br>48K              | 2K<br>2.5K                 | 2K            | 2 x 16-bit, timer,<br>2 x 8-bit timer, RTC,<br>1 x USART, 1 x UART,<br>1 x SSI / I <sup>2</sup> C, 1 x LIN,<br>1 x CAN, 12 x 10-bit ADC,<br>41 I/O + 3 Input | LQFP-48           |

| R8C25  | 16K<br>32K              | 1K<br>2K                   | 2K            | 2 x 16-bit timer,<br>2 x 8-bit timer, RTC,<br>2 x USART,<br>1 x SSI / I <sup>2</sup> C, 1 x LIN,<br>12 x 10-bit ADC,<br>41 I/O + 3 Input                     | LQFP-52<br>LGA-64 |

### ModSDKM16C Low-Cost Evaluation Kit for EUR 99,-\*

This new evaluation kit is based on the modular concept of the professional ModSDK platform. The kit contains a simple CPU module using the R8C microcontroller series, the USB-based debugger E8 and a ready-to-go package of development and application software.

+49 7249 910-523 renesas@msc-ge.com

| Viewpoint                                                             | 3  |

|-----------------------------------------------------------------------|----|

| Microcontrollers                                                      |    |

| Flexible migration with complementary                                 |    |

| 8-bit and 32-bit microcontrollers                                     | 6  |

| Interfacing a USB flash drive to a PIC microcontroller                | 10 |

| Analog & Power                                                        |    |

| Power supply sequencing with supervisor functions in PMUs             | 13 |

| Ripple management on hysteretic DC/DC controllers                     | 14 |

| Technology trends for highly efficient air conditioners               | 16 |

| Model-based Design                                                    |    |

| Model-driven design languages for real-time and embedded applications | 18 |

| Steer-by-wire system development with model-based design              | 21 |

| Tools & Software                                                      |    |

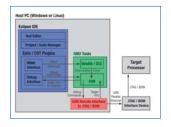

| Building an embedded cross-<br>development environment with Eclipse   | 24 |

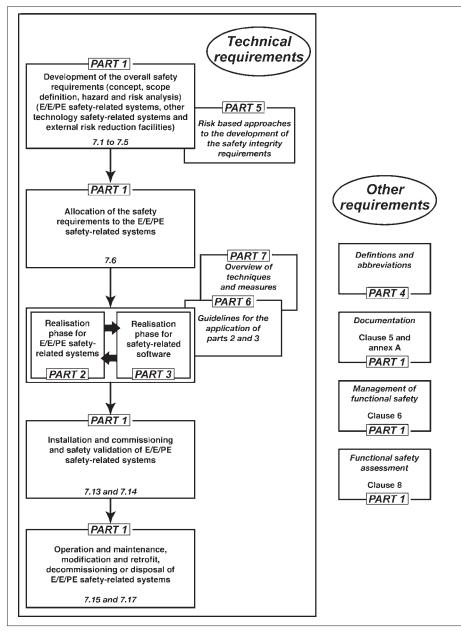

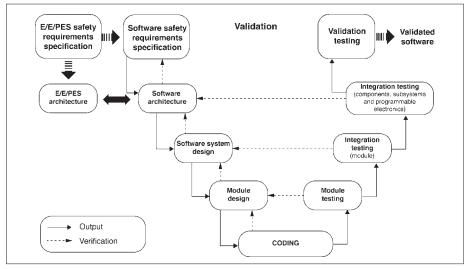

| Solid project lifecycle planning with IEC 61508 software development  | 27 |

| Asymmetric real-time multiprocessing on multi-core CPUs               | 31 |

| Building applications for network-<br>enabled Linux-based devices     | 34 |

| Connectivity                                                          |    |

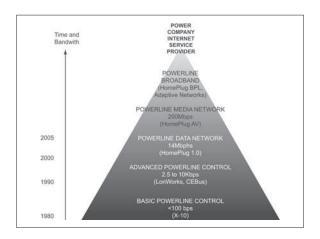

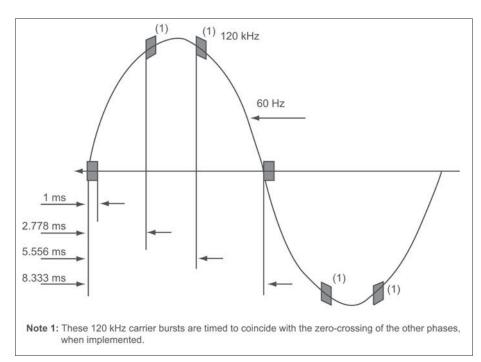

| Powerline communications – the future for smart homes?                | 37 |

| Memories                                                              |    |

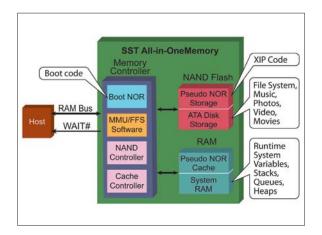

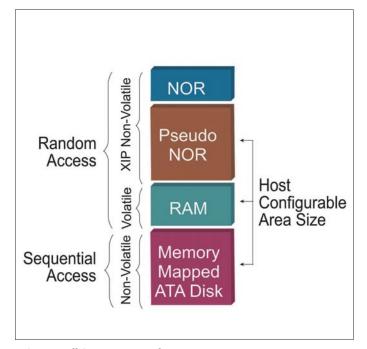

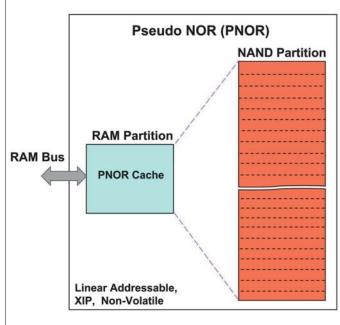

| A managed memory subsystem for embedded systems                       | 40 |

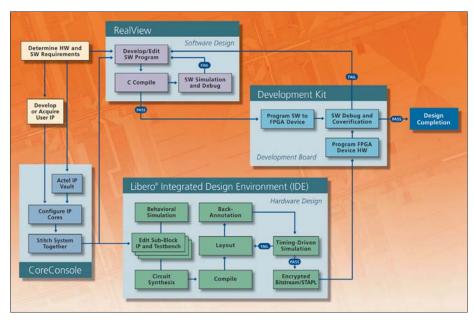

| FPGAs & SoC Design                                                    |    |

| Development tools are key to FPGA deployment in SoC designs           | 42 |

| Product News                                                          | 43 |

|                                                                       |    |

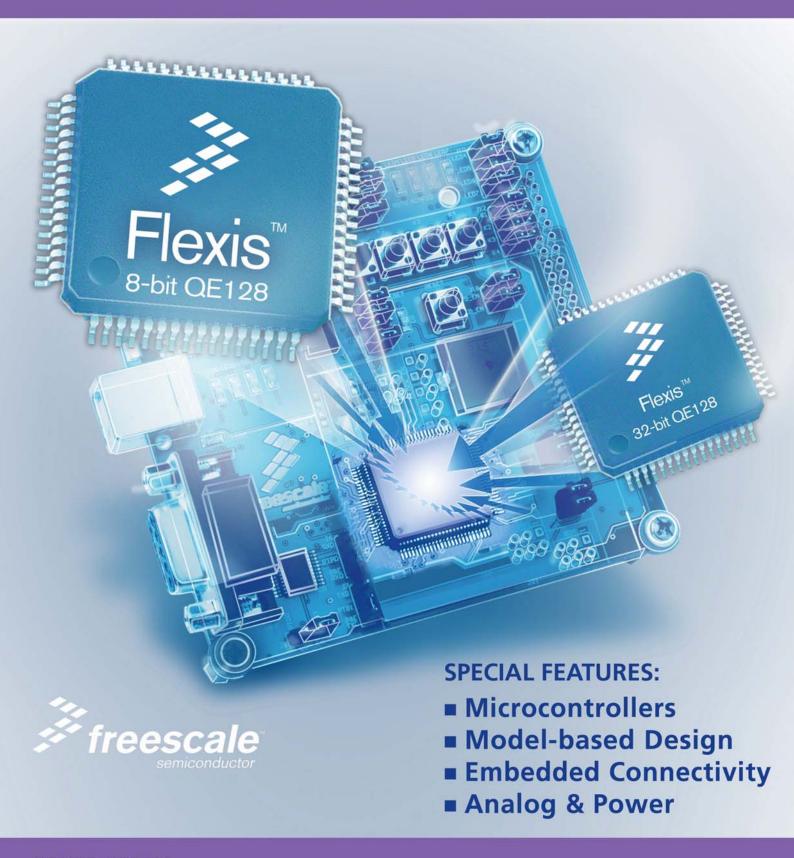

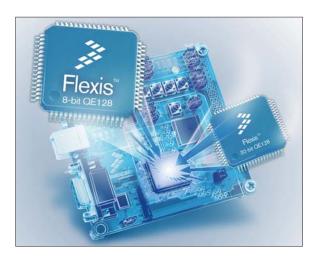

**Cover Photo**Freescale Semiconductor

### Interfacing a USB flash drive to a PIC microcontroller

**PAGE 10**

This article looks at the detailed implementation and programming of a design to link a low-cost PIC microcontroller to a flash drive via a USB2.0 full speed interface.

### Technology trends for highly efficient air conditioners PA

**PAGE 16**

This article describes the developmental trend in power electronics technology for implementing highly efficient air conditioners.

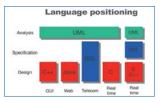

### Model-driven design languages for real-time and embedded applications PAGE 18

Model-driven engineering is an approach to software development based on abstract models of the system to be developed.

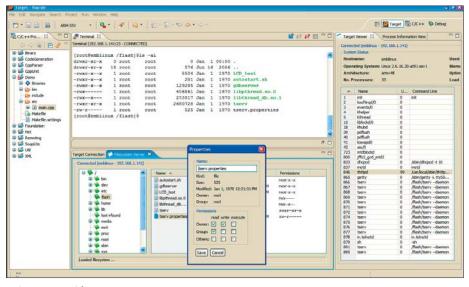

### Building an embedded crossdevelopment environment with Eclipse PAGE 24

This article describes how to construct a free or low-cost cross-development environment based on the open-source Eclipse IDE and GNU toolsets. The task can be difficult and time-consuming, but the article shows how preconfigured Eclipse projects and pre-built GNU tools help speed construction.

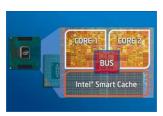

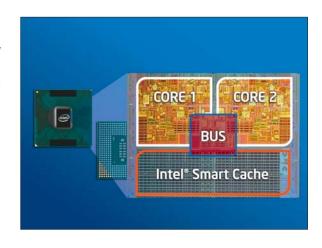

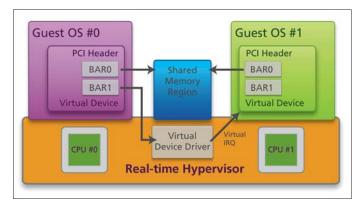

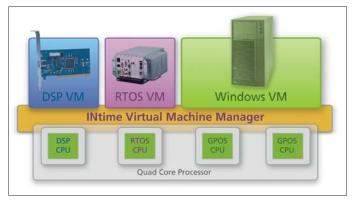

### Asymmetric real-time multiprocessing on multi-core CPUs PAGE 31

The latest multi-core processors are ideal for implementing multi-OS embedded applications. Virtualisation technology makes it possible for a multi-core system to easily support multiple operating systems on a single computer platform.

### Building applications for networkenabled Linux-based devices

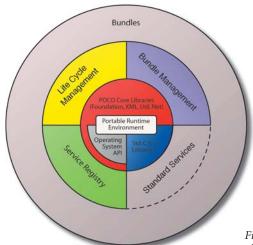

The POCO C++ libraries are a collection of portable, cross-platform C++ class libraries that can be used to create network-centric applications in technical and embedded computing. The core libraries are developed in an open source project.

**PAGE 34**

Make sure they line up for your product first!

With more than half of the product development cycle consumed by debugging, finding bugs faster means your product will get to market first.

Green Hills Software provides premier tools that pinpoint the most elusive bugs in minutes, instead of hours or days. With the MULTI® development environment's time-saving code analysis tools, errors in code are automatically found, long before the debugging process begins.

MULTI and the TimeMachine<sup>™</sup> debugger allow developers to easily find bugs so that shipping a product with known problems becomes a thing of the past.

With Green Hills Software's sophisticated technology you'll produce a better product and get it out the door long before your competition.

Call or visit us on the web **www.ghs.com** to learn more.

France: +33 (0)1 43 14 37 00 Germany: +49 (0)721 98 62 580 Israel: +972 (0)9 9584060 Netherlands: +31 (0)33 4613363 Sweden: +46 (0)46 211 33 70 UK: +44 (0)1844 267950

# Flexible migration with complementary 8-bit and 32-bit microcontrollers

### By Inga Harris, Freescale

This article introduces Flexis, which means a single development tool to ease migration between 8-bit and 32-bit MCUs, and a common peripheral set to preserve software investment with pin compatibility wherever practical.

■ The consumer and industrial markets are demanding greater energy efficiency in new product designs. Portable products need to extend battery life with each new generation, and larger products, such as white goods, require higher energy efficiency ratings to remain competitive. In many cases, replacing mechanical components with electronics improves board power consumption, and additional software control can fine-tune application power performance.

Advances in product components enable engineers to use new concepts and technologies to conquer the power use limitations of earlier products. The microcontroller (MCU) is key to these power reduction innovations for two reasons. Firstly, the MCU itself consumes power, and second, the MCU controls the other system components that also consume power. Therefore, the MCU manufacturers need to incorporate very-low-power features in their latest product designs.

From the RS08 to the highest-performance ColdFirev4 processing devices, the controller continuum provides compatibility for an easy migration path up or down the performance spectrum. The connection point on the controller continuum is where complementary families of S08 and ColdFirev1 microcon-

trollers share a common set of peripherals and development tools to deliver the ultimate in migration flexibility. Pin-for-pin compatibility between many Flexis microcontroller devices allows controller exchanges without board redesign, and the MC9S08QE128 (S08) and the MCF51QE128 (ColdFire v1) permit exactly that. Flexis means a single development tool to ease migration between 8-bit (S08) and 32-bit (CFV1) and a common peripheral set to preserve software investment between 8-bit and 32-bit with pin compatibility, wherever practical, to maximise hardware reuse when moving between 8-bit and 32-bit.

System designers have to balance the power consumption (the key parameter being Idd measured in amps) and performance (MIPS) to suit application demands. Generally the faster components are clocked, the more power they consume. In an application that is running most of the time, the most efficient solution is one that will run as slow as the system can tolerate. A motor controller is an example of such a system. If the key function is to convert a signal via an analog-to-digital converter (ADC) channel, then the ADC cannot be clocked slower than the minimum sample frequency due to Nyquists law, thus limiting how slow you can run the MCU. In many cases, the application will perform with lowest overall power by performing the scheduled tasks as fast as possible to allow the MCU to quickly revert to a very low-power state. For example, a smoke detector only needs to wake every five seconds, take a reading, make a decision and go back to sleep. This method is very common in battery-operated devices. Such systems are asleep approximately 99 percent of the time. To enable such systems, Freescale has incorporated fast clock switching and fast wake-up routines to help application designers meet their target power consumptions.

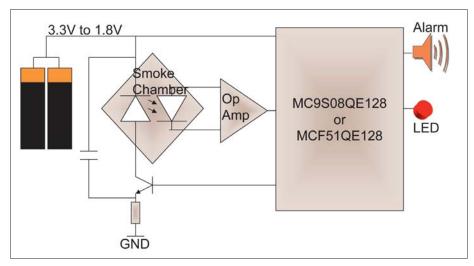

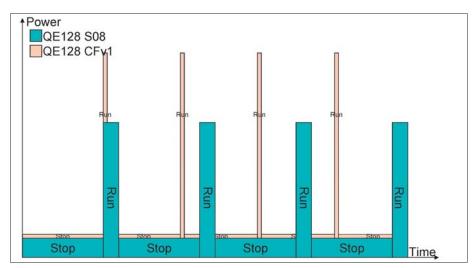

Figures 1 and 2 show a smoke detector block diagram and the power vs. time graph. The MCU has one main input from the smoke chamber and two outputs - an alarm and a LED. The real-time clock (RTC) module on the MCU can wake the device periodically from stop 2 mode to enable the op amp to take a reading and process the data to make a decision on the LED and alarm status. The MCU can then re-enter stop 2 mode to conserve power. The HCS08 has a slightly lower stop 2 mode current than the ColdFire V1 microcontroller equivalent part, but the S08 CPU has fewer built-in data processing capabilities. Figure 2 compares the power and time plots of both devices, enabling to choose the solution that best fits an application profile. In applications where task execution speed is of the utmost

Access to hundreds of thousands of quality, name-brand products available online today!\*

€18.00 flat fee for UPS (United Parcel Service). Express Air for delivery within 1-3 days (dependent on final destination). All Prices are in EURO and British pound sterling and include duties.

\*New product added daily.

© 2007 Digi-Key Corporation

### Quality Electronic Components, Superior Service

| Austria | at.digikey.com | 0800.291.395    |

|---------|----------------|-----------------|

| Belgium | be.digikey.com | 0800.78.962     |

| Denmark | dk.digikey.com | 80.88.13.67     |

| Finland | fi.digikey.com | 0800.115.281    |

| France  | fr.digikey.com | 0800.161.113    |

| Germany | de.digikey.com | 0800.1.800.125  |

| Greece  | gr.digikey.com | 00800.3122.3456 |

| Ireland | ie.digikey.com | 1.800.552.170   |

| Italy   | it.digikey.com | 800.786.310     |

| Luxembourg     | lu.digikey.com  | 800.24.398     |

|----------------|-----------------|----------------|

| Netherlands    | nl.digikey.com  | 0800.020.3710  |

| Norway         | no.digikey.com  | 800.15.286     |

| Portugal       | pt.digikey.com  | 800.831.521    |

| Spain          | .es.digikey.com | 900.983.183    |

| United Kingdom | uk.digikey.com  | 0.800.587.0991 |

|                |                 | 0.800.904.7786 |

Or visit www.digikey.com for ordering information.

701 Brooks Ave. South • Thief River Falls, MN 56701 • USA

Figure 1. Simple smoke detector block diagram

Figure 2. Power vs. time plot for smoke detector application

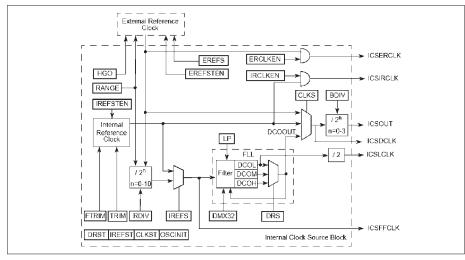

Figure 3. The heart – the internal clock source

importance, the MCF51QE128 ColdFirev1 microcontroller device may be the better solution. The pin compatibility of these two products means that migrating from one strategy to the other is quick and easy, as the same board, soft-

ware and tools can be used. The heart of the QE128s (both the S08 and ColdFirev1 microcontroller products) is the internal clock source module (ICS) as shown in figure 3. This module enables designers to select an external ref-

erence clock (ERCLK) from 32 kHz up to 16 MHz or an internal reference clock (IRCLK) that is trimmable from 31.25 kHz to 39.06 kHz. The heart of the ICS is the frequency lock loop (FLL) block which multiplies its input clock up to a maximum 50 MHz. The input clock to the FLL, also known as the FLL reference clock, must be in the 31.25 kHz to 39.06 kHz range for the FLL to operate correctly. This is simple with the internal FLL reference clock as all you have to do is trim to the correct range. The external reference clock can be as high as 16 MHz and can be divided by a reference divider (RDIV), which is programmable from one to 1024. The FLL can also be bypassed if a low-frequency bus is required. A second divider block, bus frequency divider (BDIV), can divide the clock signal down by one, two, four or eight before it is put out onto the ICSOUT signal. The MCU bus clock is ICSOUT divided by two.

The ICS also controls an independent 1 kHz very-low-power oscillator (LPO), which can be used by the RTC and the watchdog (COP). It is a feature that can be used to conform to EN60730, the standard for automatic electrical controls for household use and similar applications. There are different clock sources which can be used by each module on the MC9S08QE128. Other clocks are OSCOUT, which is a direct path to the external clock and XCLK, which is the signal going into the FLL block - either the internal oscillator or the external clock source, post RDIV. The key to the MCUs flexibility is the ability to use the internal oscillator and the external oscillator source for different modules at the same time. This means by running some modules slower than others, power consumption can be reduced. A secondary power-saving feature related to clocks has been incorporated into the QE128 design. The system clock gating control registers 1 and 2 (SCGC1 and SCGC2) gate on (1) or off (0) the clock source control the clock gating to the timers, ADC, inter-integrated circuits (I2Cs), serial communication interfaces (SCIs), debug module, flash memory, external interrupt request (IRQ), keyboard interrupt module (KBI), analog comparator, RTC and serial peripheral interfaces (SPIs). By gating off the clock to unused modules, precious milliamperes are saved in the MCU's run and wait modes. This feature is especially important on devices like the QE128 because the MCU incorporates many communications modules and timers.

Gating modules on only when needed, and gating them off when the job is done, is a significant power savings technique. The clock is gated on/off immediately after the register is written. However, this method has vulnerabilities that need to be considered:

✓ after a reset all the clocks are gated on, so to keep power consumption down the clocks

|            | Typical Bus<br>Frequency | Typical<br>Idd (S08) | Typical Idd<br>(ColdFire v1) | Exit Sources                                 | Exit Time |

|------------|--------------------------|----------------------|------------------------------|----------------------------------------------|-----------|

| Run        | 8 MHz                    | 6.5 mA               | 13.2 mA                      | n/a                                          | n/a       |

| LP<br>Run  | 16kHz                    | 22 µA                | 50 μΑ                        | Clear LP bit                                 | n/a       |

| Wait       | 8MHz                     | 1.8 mA               | 1.8 mA                       | any interrupt                                | instantly |

| LP<br>Wait | 16kHz                    | 3.3µA                | 3.3 µA                       | any interrupt                                | instantly |

| Stop 3     | n/a                      | 450 nA               | 520 nA                       | RTC, LVD/LVW,<br>ADC, ACMP,<br>IRQ, SCI, KBI | 6ns       |

| Stop 2     | n/a                      | 350 nA               | 350 nA                       | RTC, IRQ or<br>RESET                         | 29ns      |

CPU mode comparison chart

should be gated off as soon as possible,

- ✓ writes to registers associated with a gated off module have no effect,

- ✓ to avoid erroneous operation, it is good practice to disable the module before gating it off and reinitialize it when the module is gated back on.

As described, the ICS is routed to all the power consuming and component controlling peripherals. This allows designers to choose the power reduction and performance levels they need. All other factors being equal:

- ✓ using the low-range, low-gain external oscillator is more power economical than using the internal circuitry,

- ✓ bypassing the FLL, or phase-locked loop (PLL), will save power by reducing the frequency as well as the power saved bypassing the FLL circuitry, and

- ✓ it is possible on the QE128 MCUs to disable rather than bypass the FLL for further power reduction.

Note that when choosing between the PLL and FLL, the FLL is the lowest power option, although it is less accurate in the long term.

The ICS on the QE128 MCU has six modes of operation: FLL engaged internal (FEI), which is the default mode; FLL engaged external (FEE); FLL bypassed internal (FBI); FLL bypassed external (FBE); FBI low power (FBILP) and FBE low power (FBELP). Each is activated by the LP bit in ICS control register 2. FBILP and FBELP reduce the voltage swing on the oscillator tracks, lowering overall power consumption.

Choosing the right mode for the right stage of the system design can make or break the power consumption targets. The days of simply having the choice of a run mode and a low-power mode are over, as the latest generations of MCU products have a variety of modes with various compromises and advantages. Exit paths, wakeup times and register retention are all choices that you have to make. Along with the usual run mode, the QE128 has five other power saving modes. Three of them, wait, stop 3 and stop 2, are not new to the S08 core and are common in other cores, although they may be under different names.

In wait mode the CPU shuts down purely to conserve power. The MCUs system clocks and full voltage regulation are maintained. Wait mode saves between 30 to 60 percent of the run mode current, depending on the bus frequency, and any interrupt will allow wait mode to be exited instantly. Stop modes halt the system clocks and place the voltage regulator into standby. Stop 3 on the QE128 MCU consumes the highest power of the two stop modes and has the advantage of allowing a wake-up time of just 6ns. There are three versions of stop 3: with BDM enabled, with the voltage regulator active, and with no frills.

Unlike wait, exit from stop 3 is limited to the RTC, low voltage detect/low voltage warning (LVD/LVW), ADC, analog comparator with internal reference (ACMP), IRQ, SCI, KBI and Reset. Stop 2 is the name of the lowest power mode on the QE128 MCU. The internal circuits are powered down while still maintaining the RAM contents and the pin states. The major difference is that there are only three ways to get out of the mode - reset, IRQ and RTC. The MCU resets upon exit in the same manner as a power-on reset.

There are two new power-saving modes on the QE128 device - low power run (LPR) and low power wait (LPW). LPR saves power compared to normal run mode by placing the voltage regulator into standby. To enter this mode, FBELP, the lowest power ICS mode, must be running. The low-voltage protection system must be disabled along with the MCUs internal bandgap and the on-chip in-circuit emulator/ background debug controller (DBG/BDC) modules, as all three modules consume significant

amounts of power, regardless of the bus frequency. Since the voltage regulator is in standby, every opportunity to keep the power down in this mode is recommended.

Low power wait (LPW) mode can only be entered from LPR mode and as such the restrictions on LVD circuitry, debugging and ICS mode are the same. The MCU can typically save 50 percent of its current consumption in LPW versus LPR. The table compares the key characteristics of the CPU operation modes.

The QE128 MCU has flash memory which is reprogrammable down to 1.8V, which helps extend battery life in portable applications. Three ports on the QE128 device have set, clear and toggle capabilities, which can speed up pin manipulation, reducing code execution time so low-power modes can be re-entered quickly. All the devices output pins have slew rate control which, when driving external components, can reduce power by slowing transients and drive strength control.

### **Product News**

#### Renesas to develop new CPU architecture for MCUs

Renesas announces that it is in the process of developing a new CPU architecture and will offer two CPUs based on this new architecture to address 16- and 32-bit markets, while maintaining compatibility with Renesas existing MCUs. The new architecture will have innovative advances over the M16C and H8S 16-bit CPUs and R32C and H8SX 32-bit CPUs that Renesas currently offers, while offering compatibility with the existing families in terms of CPU instruction sets, peripheral register sets and development tools.

News ID 263

### Atmel: customizable microcontroller-based SoC platform

Atmel announces a CAP microcontroller-based system-on-chip platform for complex applications that require fast time-to-market. CAP features high-speed local memory, a wide range of industry-standard peripherals and interfaces, and a high-capacity metal programmable block that allows the designer to add a significant amount of custom logic on-chip. CAP is based on Atmel's Metal Programmable Cell Fabric that provides nearly identical routed gate densities to those of standard cells in the same process.

News ID 264

# Interfacing a USB flash drive to a PIC microcontroller

By Fred Dart, Future Technology Devices International (FTDI)

■ This article looks at the detailed implementation and programming of a design to link a low-cost PIC microcontroller to a flash drive via a USB2.0 full speed interface.

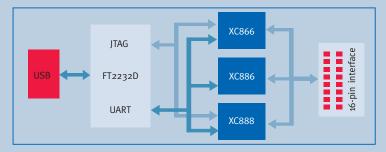

USB interfaces are everywhere today, with lowcost flash memory drives and all kinds of USB peripherals being readily available, but these are very much focused on the PC market. Attempt however to make use of these peripherals in the 8- and 16-bit embedded market, and you find that implementation, cost and power consumption become major considerations. Part of this is down to the embedded controllers that are used in such systems. Devices such as the PIC family of controllers from Microchip are widely used with a broad range of memory densities and peripherals, but they lack the interfaces, resources and performance to incorporate a USB host controller. In this example application, a VNC1L Vinculum controller provides the interface between the PIC as the system controller and a USB2.0 full speed port. This allows a USB flash memory drive connection, for example, to be accomplished with a minimum of implementation time and overhead.

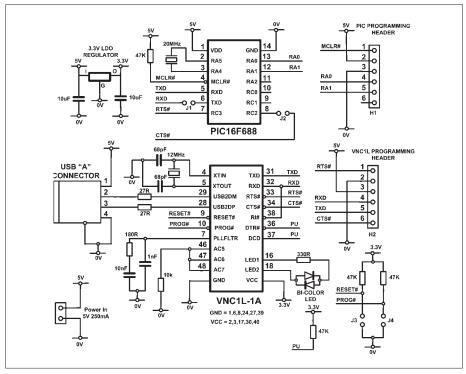

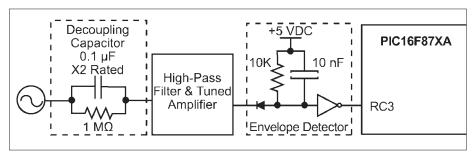

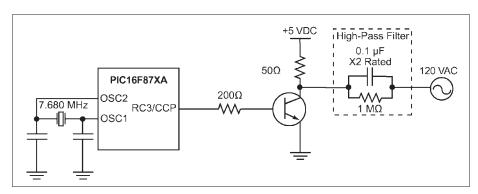

The controller is based around a custom processor core, with twin direct memory access (DMA) engines to accelerate data transfers and a 32-bit numeric co-processor to optimise the calculations for the file system - all in a single chip with 64 kbytes of embedded flash program memory and 4 kbytes of internal data SRAM. Vinculum is specifically targeted at the embedded USB controller market and requires a minimum of external support components. One key feature of the Vinculum core is that its code length is significantly reduced compared with common MCU cores. Reducing the code overhead of the core allows much more functionality to be squeezed into the on-chip e-flash memory. Such features are complementary to a PIC-based embedded system. The schematic of such a system is shown in figure 1, using Vinculum to link a small PIC MCU to a USB "A" connector and hence to a USB flash drive

The PIC is the controller of the system, taking data from sensors or other sources via its general purpose I/O pins (RC0, RC1, RA2 on pins 9,10,11), converting the data format and writing that data in a stream to a file on the flash drive. Commands and data are sent via TXD (pin 6) to the VNC1L RXD (pin 32). VNC1L handles the FAT 12/16/32 file creation and data storage on the USB flash drive communicating with the drive via USB2DM and USB2DP on pins 28 and 29. Data is read from the flash drive via the same pins, and sent from the VNC1L TXD (pin 31) to the RXD (pin 5) of the PIC for use by the system firmware.

The system is controlled by the firmware on the PIC, with the transfers controlled by instructions issued by the PIC and interpreted by the standard firmware on the Vinculum. Whilst that is a simple description of the system, more is required to complete the design. The devices

need power, crystals to control their clocks, and they need to be programmed. Using a 20MHz crystal on pins 2 and 3 of the PIC allows for higher baud rates of up to 115200 bit/s in its UART interface as opposed to the maximum 9600 bit/s achievable by using the internal 8MHz oscillator, thus improving the performance of the system.

PIC I/O pins RC2 and RC3 are used by the PIC firmware to simulate RTS/CTS handshake signals with the VNC1Ls UART interface. A 5V regulated PSU at 250mA is required, providing up to 200mA at the USB "A" connector, 25mA to power the VNC1L and 25mA to power the PIC16F688. VNC1L requires a 3.3V supply which is provided by a 3.3V LDO regulator, and has 5V tolerant I/O pins which enable it to connect to the PIC without using level shifters. For low-power applications the VNC1L can be put into a 2mA sleep mode when not required. To

PIC microcontroller and Vinculum USB interface chip

# Enjoy the benefits of field-oriented control at lowest system cost

I N F I N E O N is the world's first microcontroller supplier to offer optimized 8-bit MCUs capable of supporting Field Oriented Control (FOC), a technique for operating electric motors that results in smooth and efficient operation at all speeds. Implemented on its 8-bit XC886 and XC888 families, Infineon brings FOC motor control solutions to price-sensitive applications such as dishwashers, fan controls and washing machines. This highly innovative solution offers significant reduction of system costs and frees up to 40% CPU capacity, providing plenty of headroom for other applications. Unlike most competitive hard-coded FOC implementations, the XC886/8 microcontroller-based solution offers the added benefit of software reprogrammability to give developers more versatile application options.

### Field Oriented Control

### Key features of XC886/888 enabling FOC

- 16-bit fully programmable co-processor (vector computer)

- PWM unit with hardware trigger for A/D conversion (CapCom6E)

- A fast 10-bit A/D converter

#### Key benefits

- 16-bit performance at 8-bit costs

- Higher energy efficiency

- Lower torque ripple

- Excellent dynamic response

Order now at:

www.infineon.com/xc8oo-foc

wake up the device, strobe the ring indicator pin (RI, pin 38) of the UART interface. If this is connected to the RXD line, as here, it can be triggered by an incoming dummy command to wake up the device. This design also includes a bi-colour status LED indicator powered from pins 16 and 18. This indicates successful enumeration of the USB flash drive and access to the file system. The ViNC1L is programmed with standard firmware, called VDAP (Vinculum Disk and Peripheral) that interprets the commands coming from the PIC. These VDAP commands are DOS-like instructions such as DIR, RD and WR. The command set also supports single byte hex commands which are more suited to control by a microprocessor. VDAP commands are included in the PIC firmware to control access to the USB flash drive. A typical sequence would be to create a

file, read/write data to the file and then close the file. This design contains two programming headers, one for each device assuming that a development environment is desired. For a production design, both devices could be pre-programmed prior to insertion on a PCB, thus eliminating the headers and jumpers.

During normal operation, J1 and J2 should be populated and the other jumpers left open. To program the VNC1L, remove J1 and J2 jumpers to isolate the VNC1L UART inputs from the PIC outputs. Disconnect the 5V PSU and then connect a TTL-232R-3V3 cable to H2. Connect the USB side of this cable to a PC with the VPROG programming utility installed. Populate J4 to pull the PROG# pin of the VNCL1A low and temporarily short J3 to reset the device and put it into programming mode.

After programming, remember to restore the jumper settings to the operational positions. The programming header for the PIC connects to pins RA0 and RA1 and MCLR# of the device, with the 5V programming voltage/supply being supplied via the header. Disconnect the 5V PSU prior to programming the PIC microcontroller.

The header would be connected to a standard PIC development environment such as a PICK-it2, allowing Microchips debug and downloading tools to be used. In the sample C code provided the PIC waits for a flash disk to be detected and then opens a file called hello.txt. The text "Hello World" total with a carriage return and line feed characters are then written to the file. It then closes the file and waits for the disk to be removed.

### **Product News**

### Microchip: 8-bit microcontrollers with integrated LCD control

Microchip announces six new members of its 8-bit PIC microcontroller family featuring an integrated LCD control module. The PIC18F85J90 family doubles the amount of Flash and RAM memory available in 64- and 80-pin PIC18 LCD devices. This increased memory enables to add more complex functionality, such as speech playback, while taking advantage of the cost savings offered by the PIC18 J series 3-volt manufacturing process.

News ID 296

### Gleichmann: 8-bit MCU family with LCD controllers/drivers

NEC Electronics 8-bit 78K0/Lx3 microcontrollers (MCUs) include on chip controllers/drivers for 88 to 288 LCD segments. The MCUs are available with 8 Kbytes to 60 Kbytes of embedded flash memory and RAM from 512 bytes to 2 Kbytes, in pin counts ranging from 48 to 80.

News ID 306

#### ST: 32-Bit MCU family powered by ARM Cortex-M3 core

STMicroelectronics has announced a family of 32-bit Flash microcontrollers based on the ARM Cortex-M3 core - a core with features specifically designed for embedded applications requiring a combination of high performance (1.25 Dhrystone MIPS/MHz), low power and low cost. The STM32 family benefits from the

Cortex-M3s architectural enhancements including the Thumb-2 instruction set to deliver improved performance combined with better code density, and a tightly-coupled Nested Vectored Interrupt Controller for significantly faster response to interrupts, all combined with low power consumption.

News ID 343

### Atmel: application processor for Linux-based designs

Atmel announced the AT32AP7001, a member of the AVR32 AP7 family of application processors optimized for cost constrained, Linux-based embedded designs. The device is packaged in a 30 x 30mm VQFP for easy integration into a four-layer PCB design. The processor is built around the AVR32 AP7 application processor core and offers 210 Dhrystone v2.1 MIPS when clocked at 150 MHz and powered at 1.8V (1.4 DMIPS/MHz), with an active power consumption of 75mA (500  $\mu$ A/MHz).

News ID 320

#### Renesas: extended M16C microcontroller platform

Renesas announced 12 different M16C/64 group models and 20 different M16C/65 group models for car audio, home audio, and similar consumer products as well as industrial applications, as additions to the M16C Platform microcontroller lineup. These models are up-

graded functions and performance extensions of the current M16C/62P group and are compatible with current M16C Platform products, offering flexibility in implementing system functional enhancements and version upgrades.

News ID 352

#### ST: new version of ARM9-based flash microcontrollers

STMicroelectronics has announced the release of a new version of its 32-bit ARM9-based STR910F flash microcontrollers The enhanced memory accelerator in the STR910FA boosts performance by allowing the burst Flash memory to stream instructions more freely to its ARM966E CPU core. Peak performance remains the same, at 96 MIPS during the execution of sequential instructions, but the average performance has increased significantly when instructions are non-sequential, as a result of the larger memory accelerator.

News ID 368

### MIPS: synthesizable 32-bit processor surpasses 1 GHz

MIPS announces the MIPS32 74K cores, fully synthesizable 32-bit processors that achieve operating frequencies greater than 1 GHz in TSMC 65nm process technology. Broadcom has already taken the first license of this innovative design with advanced microarchitecture, enhanced DSP capabilities.

News ID 269

ore information about each news story is available on www.embedded-control-europe.com/ece\_magazine You just have to type in the "News ID".—

# Power supply sequencing with supervisor functions in PMUs

### By Todd Vanyo, Texas Instruments

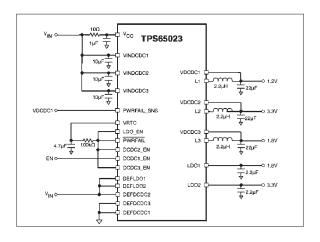

This article discusses the building blocks needed in a multi-channel power management unit (PMU) to implement the supervisor functions, and provides an example using the TPS65023 to sequence the DaVinci processor family.

Figure 1. Sequencing schematic of the TPS65023 pins

■ Most processors, from simple 8-bit microcontrollers to the latest multicore microprocessors, require some form of power supply sequencing. Power supply supervisors have long existed to help solve this problem. But with cost and space at a premium in the ever-increasing number of consumer products containing processors, supervisor ICs may not be welcome. Basic supervisor functions can be implemented with a PMU if the proper building blocks are available. Supervisor ICs are not complicated devices. The basic unit of information is the output of a comparator, which compares an input voltage to a fixed reference voltage - usually generated internally to the supervisor. When the comparator output is low, the supervisor reset output is held in some state (typically low). A timer is started when the input voltage rises above the internal reference and the supervisor reset output changes state when the timer finishes. The timer could be based on the fixed count of an oscillator or the voltage on a capacitor - the latter making the timing variable. The output of the supervisor is usually tied to the reset of the processor or the enable of another power rail.

Supervisor ICs come in a number of different combinations – single voltage sense, multiple voltage sense, fixed reset time, variable reset time, etc. All these provide options for the system designer when designing the sequencing.

But incorporating sequencing costs money and board space - it is another part to purchase and place on the board. This leads to the question of how this function can be implemented in a more cost-effective way. The power supply is the best place to implement sequencing. If the PMU design targets a specific processor, internal logic may already exist to sequence each rail as required. In this case, a single enable input to the PMU may trigger a sequence of events that leads to each rail becoming available at the right time. Even a general purpose PMU that is processor agnostic can implement the necessary sequencing, as long as the same supervisor building blocks are available. The TPS6502x family of PMUs has these elementary building blocks available.

There are as many sequencing requirements as there are processors. Some require that the memory and I/O voltage be available before the core voltage and some are the exact opposite, requiring that the core voltage be available first. One positive aspect is that sequencing requirements have become more forgiving and do not require the amount of time they once did. As long as the building blocks are available in the PMU, the necessary sequencing should be possible. By way of example, let's look at the DaVinci family of processors. The only hard sequencing requirement is the need for the ARM microcontroller core (1.2V domain) to come up

before the memory and I/O domains (1.8V & 3.3V). The memory and I/O voltages may be come up in any order, even together, after the ARM core is powered. The DaVinci reset signal, /RESET, must be held low until all three voltage domains are fully up. To eliminate the supervisor for this processor line, the PMU must have at least one comparator with an internal reference voltage to monitor the core voltage. It must also have a means of signaling that all three rails are fully up.

The TPS65023 has two independent and standalone comparators - one with the input LOW-BAT\_SNS and output /LOWBAT, one with input PWRFAIL\_SNS and output /PWRFAIL. The internally generated reference is 1V  $\pm 1\%$ . The outputs are the open-drain inversion of the comparator output. One comparator is all that is needed for the DaVinci processors, as the memory and I/O can be ganged together. Using two comparators allows you to sequence three rails separately. In addition to the comparator, you need some way to determine that the rails have reached the proper voltage. PMUs accomplish this with an output that indicates that all enabled outputs are within some regulation range. The TPS65023 consists of three step-down converters and two linear regulators that default to the voltages needed by the DaVinci family of processors. Each converter has a Power Good comparator enabled

when the converter is enabled and toggles when the output voltage is 95% of the target voltage. The /INT pin is an open drain output that is the logical AND of the Power Good comparator outputs for each enabled converter. When a converter is enabled and its output voltage is more than 10% below the target voltage, the /INT pin will be pulled to ground. To fulfil the DaVinci sequencing requirements, the 1.2V output from the TPS65023 must be up before the 1.8V and 3.3V outputs. One way to achieve this would be to connect the DCDC1 output directly to the DCDC2\_EN, DCDC3\_EN, and LDO\_EN inputs. However, the digital VIH of these input pins is 1.2V minimum, which means there will be insufficient headroom in the event of transients on the

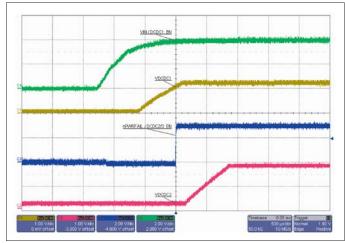

DCDC1 output. This is a common issue and the VIH voltages should be carefully checked. Instead of tying the output of the DCDC directly to the other enables, one of the comparators described can be used to compare the 1.2V output to the internal 1V reference voltage. With the output of the comparator pulled up to a voltage that is always present (such as the voltage needed to power an RTC) and tied to the other converter enables, the sequencing requirements would be met. Figure 1 gives a schematic view of the connections to get the necessary sequencing (note that not all TPS65023 pins are shown, only those needed for sequencing the converters). Figure 2 shows the scope trace of the power up of DCDC1 and DCDC2 using the connections in figure 1.

The DaVinci reset requirement, that the /RESET input be held low until all the voltages are available, can be met by using the Power Good logic that drives the /INT pin on the TPS65023.

Since /INT will stay low when an enabled converter is out of regulation, the /INT pin can be pulled up to the 1.8V converter (/RESET on the DaVinci family is a 1.8V input) and tied directly to /RESET. This works because the /INT pin will be low while DCDC1 ramps up. When DCDC1 hits approximately 1V (still below valid regulation), DCDC2 and DCDC3 are enabled – thus holding /INT low until all converters are within regulation. Figure 3 shows the scope trace with the /INT signal (labeled nINT).

# Ripple management on hysteretic DC/DC controllers

### By Ernest Bron, National Semiconductor

This article discusses ripple. Why it is required with Constant On-Time controllers? What impact has it on the output voltage rail? How can a system be designed that has ripple, but with a minimum of negative side effects?

■ Over the last few years numerous hysteretic type DC/DC controllers have been introduced to the market place. Hysteretic control requires no loop compensation which makes them relatively easy to design with. A major disadvantage however is the fairly unpredictable

operating frequency combined with the inherent need for an output voltage ripple. The introduction of Constant On-Time (COT) controllers largely eliminated the frequency issue. However basic control in COT-type controllers is still voltage-based, hence a ripple is still required. The basic principle of COT-type controllers revolves around sensing the output voltage ripple and switching the FETs appropriately. A typical controller requires about 10mV of ripple on the feedback pin. To show the effect of this requirement on the output

voltage regulation, assume we have a step-down regulator with a feedback voltage of 1.2V and an output voltage of 5V. Here 10mV ripple on VFB translates to about 42mV of output voltage ripple on the 5V output (about 0.8%). This would not normally be problematic for a typical 5V system, however as output and feedback voltage requirements decline, ripple becomes more of an issue. We do the same calculation for a system with 0.8V feedback voltage and 1.3V output voltage, still assuming a minimum ripple of 10mV on VFB. On the output rail we

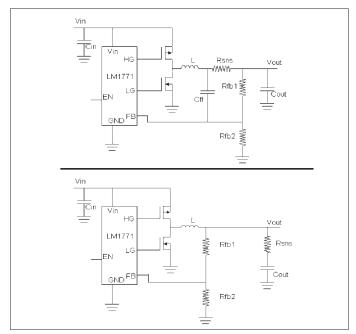

Figure 1. The two basic principles for ripple creation: The top circuit is suited for high output voltage and low output currents. The bottom circuit is suited for low output voltages.

Vin

Cin

HG

LM1771

Crip

Crip

Crip

Crip

Rfb1

Cout

Rfb2

Figure 2. This block diagram shows a circuit that can inject ripple onto the feedback pin with minimal impact on either efficiency or output voltage ripple.

now see a minimum ripple requirement of 16.5mV, or about 1.3%. Combine this with the fact that lower power rails typically require even tighter voltage regulation, and we see ripple does indeed become an issue.

Apart from this, there is also the fact that a design using a COT controller needs to make sure there is a ripple on the feedback pin to start with. Normally ripple is generated by the application load current in conjunction with the output capacitor and its associated equivalent series resistance (ESR). Therefore, a COT controller, or any hysteretic-based controller for that matter, will have a hard time operating properly if the output capacitor has low ESR. Here lies the core of the problem for many designs, because in many cases the use of ceramic capacitors is a must.

Because ceramic capacitors are low cost and offer very low ESR, which helps in reducing voltage spikes in the system, they have become the prevalent capacitor type of choice to use. Most modern power conversion devices such as LDOs or DC/DC controllers have their internal control loop optimised for operation with low ESR output capacitors like ceramic capacitors. Hysteretic-based controllers still require a ripple to function though. To make them work with ceramic capacitors we need to create a ripple. The easy way to create ripple is to 'add' ESR to

the output capacitor. Refer to figure 1. Here we see the LM1771, a recently released synchronous COT step-down regulator. It is a good example of all the advantages of using COT-based controllers. The part automatically adjusts the ontime inversely with the input voltage, making the operating frequency constant over input voltage. Because there is no need for loop compensation, there are also no associated pins. The result is a very small-form-factor, easy-to-work-with step-down controller, with very few pins and constant operating frequency.

There are two basic principles for ripple creation which are also discussed in the datasheet. If the output voltage is relatively high (compared to VFB), the top circuit of figure 1 can be used. Here Rsns is placed in series with the inductor to add ripple to the output. Together with Cff ripple it provides ripple to the feedback pin without generating additional voltage ripple or DC offset at the output. In effect Cff provides a low impedance path for the high frequency ripple to go directly to the feedback pin. Care needs to be taken with respect to output currents. As output currents increase the power loss in Rsns is no longer irrelevant. This circuit should be limited to designs with output currents of 2A or less. As the output voltage decreases, the top circuit of figure 1 starts having problems because now the ripple on the output becomes more prevalent. Since the output voltage ripple is out of phase with the ripple directly injected by Cff this causes problems. We now need to move over to the configuration as shown at the bottom of figure 1. Here Rsns is placed directly in series with the low ESR ceramic output capacitor. Ripple in induced by the additional resistance and feed via the feedback circuit (RFB1/RFB1) into the feedback pin. No more need for Cff, but as discussed, we do now see the entire required ripple on the output voltage rail. In effect we are emulating the use of a non-ceramic capacitor with higher ESR. Depending on the application, this may or may not be an issue.

The circuit shown in figure 2 illustrates an alternative to the more commonly provided solutions from figure 1. It offers ripple injection combined with little loss of efficiency and low output voltage ripple. Here ripple is injected from the FET/inductor node. Crip provides a low impedance AC path for current to flow towards the feedback pin. Rrip sets the current level and Cff integrates that current into a voltage ripple placed on top of the DC feedback voltage. There are advantages to this alternative configuration. Firstly there is no additional resistance in the main power path, meaning minimal efficiency loss. Secondly there is no series resistance on the output capacitor, allowing output voltage ripple to remain as low as possible. ■

### **FREE Subscription to ECE magazine**

Ensure getting your personal copy of ECE magazine free of charge by completing the online form at: www.embedded-control-europe.com/ece\_magazine

July 2007

# Technology trends for highly efficient air conditioners

### By Guho Jung, DaeWoong Chung, and BumSeok Suh, Fairchild

This article describes the developmental trend in power electronics technology for implementing highly efficient air conditioners.

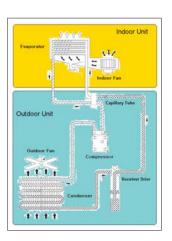

Figure 1. The structure of the general separated type of air conditioner

■ Home air conditioners are generally divided into two types, the window type and the separated type. In the former all the functions are implemented in one unit, while in the latter the indoor and outdoor units are separated. However, the specifications of air conditioners have recently been upgraded and now cover systems. In the air conditioner system, several indoor units are connected to one outdoor one for installation in large houses and offices. The greatly increased cooling capability has caused summertime power breakdowns due to the excessive use of instantaneous electric power. Consequently tremendous efforts to improve energy efficiency have been made to solve this problem. Additionally, high efficiency is an important factor in the process of replacing CFC refrigerants with natural ones to eliminate the environmental pollution problems caused by CFC refrigerants.

In this situation, each country has tried to tighten its energy regulations. For example, the U.S. Department of Energy announced an enforceable seasonal energy efficiency rating (SEER) standard of 13 for residential central air conditioners which started in January 2006. This represented a 30 percent increase in energy efficiency compared to the previous 10 SEER standard. Meanwhile the Japanese government has announced the need for 20% higher efficiency than present levels in order to meet the Kyoto

Protocol from 2010, particularly in air conditioners and refrigerators. This means energy saving through high efficiency has become a pivotal consideration in the world of air conditioners, and numerous technologies are currently being developed in response. Moreover new technologies are being developed for reducing noise and vibration generated by outdoor equipment, and network technology is being applied to the air conditioner system. However, the power-saving technologies are the primary concern of this article.

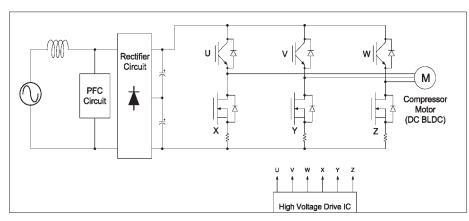

Figure 1 shows the structure of a general separated type of air conditioner and the principle of the typical refrigerants circulation cycle. In outdoor units, refrigerants at low pressure are compressed and the resulting heat is radiated away. In indoor units, the ambient heat is absorbed into radiated refrigerants by an evaporator. In this structure the compressor and fan are directly related to the electrical power. The compressor consumes the largest amount of energy of the two. A highly efficient air conditioner is implemented by performance improvement of the heat exchanger and compressor. The performance of the heat exchanger is improved by improving such mechanical technologies as the structure of radiation fin, cooling fan and flow design. On the other hand, motor design and control technologies are needed with designing the compressor, which consumes extremely large amounts of electrical power. The motor for the compressor is located in a compressor with high internal pressure and so the actual installation condition is poor. Singlephase induction motors, robust and needing no control, have been applied for most compressors up to now. But improving efficiency using single-phase induction motors has reached its limit. As an alternative, the BLDC motor (brushless DC) has been applied for highly efficient compressors, its efficiency being higher than that of the single-phase induction motor. But when the inverter efficiency is taken into consideration, the overall efficiency of the BLDC motor and inverter is almost the same as a single-phase induction motor.

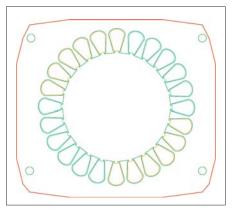

The reason for applying the BLDC and its controller to the compressor in spite of its higher material cost is that high efficiency can be obtained by using the variable speed capability over the entire operating range. The variable speed operation is possible by using a three-phase induction motor and inverter. However, the power efficiency in low-speed operation is reduced abruptly in that case and so there is a limit in making a highly efficient compressor using a three-phase induction motor and inverter. Figure 2 shows two different slot shapes of stator used in the distributed and concentrated wiring method. In the first approach to applying a BLDC motor to the compressor, the

Figure 2. Stator structure of BLDC motor in compressor: (left) distributed wiring method, (right) concentrated wiring method

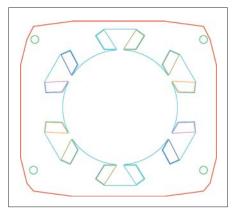

Figure 3. A new inverter using super junction MOSFET

stator wired by distributed wiring method shown in Figure 2a and the two-phase excitation by a rectangular method are mainly adopted. This rectangular method can be implemented by a simpler controller structure compared to the sinusoidal method for driving a PMSM (Permanent Magnet Synchronous Motor), and so was appropriate for home appliance products sensitive to material costs. However, the stator wired by the concentrated wiring method illustrated in figure 2b resulted from strenuous efforts to raise efficiency and cut the product cost by simplifying the manufacturing process. This type of BLDC motor is now increasingly used as standard technology in Japan by air conditioner manufacturers. Even though the concentrated method has some advantages in high efficiency and simplification of the manufacturing process, increased torque ripple has a bad effect on the compressor vibration. To solve this, a partial three-phase or sinusoidal three-phase excitation method is currently being adopted. The best result can be obtained by using conventional vector control, but it is not easy to implement due to the limit imposed by material costs. Accordingly, a partial three-phase excitation method or tuning table method for achieving an output pattern similar to vector control is being tried when large torque ripple arises.. A highly efficient variable speed motor such as a BLDC is used for a highly efficient system in applications with indoor and outdoor cooling fans. However, its contribution to energy savings is smaller because these parts consume relatively less power than the compressor. The energy-saving standard in air conditioners has changed following the JIS (Japan) revision in 2005. Since most air conditioners operate at about half rated capability, energy consumption efficiency at this actually used region is much more important than at the rated one.

Also, inverter efficiency depends on the performance of the power switching device used. So a new highly efficient inverter technology using a super junction MOSFET structure with low on-resistance as the switching device has recently been developed. Figure 3 shows the power circuit of the proposed new highly efficient inverter using the super junction MOSFET. The circuit uses an IGBT for the upper-side element and super junction MOSFET for the lower-side element. By applying a 2-phase modulation method, the low-side current conduction rate can be much higher than the high-side, resulting in a sufficient improvement in efficiency.

Power factor correction circuits are needed for power efficiency improvement, reliability improvement, and compliance with IEC international harmonics regulations. There are two types of PFC, active and passive. In this article, two active methods, partial switching and full switching PFC are explained because they have been popular in several air conditioner applications. In the waveforms of partial switching PFC, the first objective for deciding the IGBT on- time is to pass the harmonic regulation of AC input current. A first idea is to use a lookup table for the IGBT on-time according to the output power. The output power is calculated as below by the product of three-phase voltage and current vectors.

Pout = Vas\*Ias + Vbs\*Ibs + Vcs\*Ics.

When the look-up table is used, the DC link voltage is around 280V under a full range of load conditions. The circuit for full switching PFC is the same as that of partial switching PFC. However the input current has sinusoidal waveform due to pulse width modulation (PWM) at high frequency.

### **Product News**

### Linear Technology: 14-bit 2.8Msps ADC for automotive

Linear Technology introduces the LTC1403AH, a 14-bit, 2.8Msps SAR ADC guaranteed over the automotive -40 C to +125 C temperature range. The LTC1403AH operates from a single 2.7V to 3.6V supply, draws only 14mW at 2.8Msps, and is available in a tiny 10-lead MSOP package.

News ID 255

### LTC: USB power manager with three integrated buck regulators

Linear Technology announces the LTC3555, a multi-function power management solutions for Li-Ion/Polymer battery applications. The LTC3555 integrates a switching PowerPath manager, a standalone battery charger, an ideal diode, I2C control, three high efficiency synchronous buck regulators plus an always-

on LDO, all in a compact, low-profile 4mm x 5mm QFN package. The LTC3555's Power-Path control feature seamlessly manages power flow between an AC wall adapter or USB port, Li-Ion battery and system load while its 'instant-ON' operation ensures system load power even with a dead or missing battery.

News ID 240

17 July 2007

# Model-driven design languages for real-time and embedded applications

### By Emmanuel Gaudin, PragmaDev

Model-driven engineering is an approach to software development based on abstract models of the system to be developed.

■ The best-known MDE approach is the model-driven architecture defined and registered by the object management group (OMG) in 2001. Another well-known approach is model-driven design (MDD) where the focus is narrowed in order to work on a more precise model. A model-driven approach distinguishes three types of models: an abstract model of the system under development called the platform-independent model (PIM), a model defining the platform called the platform definition model (PDM), and an implementable model of the system called the platform-specific model (PSM). The PIM is the system under development and the PDM defines the rules to transform the PIM into a PSM. So in practice the team works on the PIM, the PDM is defined by the application domain or the company, and the PSM is automatically generated out of the PIM and the PDM.

To be efficient, the PIM must be abstract enough to be independent of the platform on which the system will be implemented, but at the same time it should be precise enough to be translated into a PSM. So in order to successfully translate the model, the PIM relies on a virtual machine the characteristics of which are a number of basic services and a semantic strong enough to be expressive. In the 80s, the International Telecommunication Union standardised a language to describe telecommuni-

cations protocols: the specification and description language (SDL), under reference Z.100. The main goal was to describe the protocols in an unambiguous way so that all manufacturers' implementations of a standard protocol would be compatible with each other (e.g. a Nokia GSM phone would work with an Ericsson base station). The European Telecommunications Standardisation Institute has extensively used SDL to describe telecommunication standards and it is obvious to state that compatibility has been successfully achieved. The SDL standard is regularly updated and major new versions have been produced every four years since 1984. The 1988 (SDL '88) version was considered to be the first usable version, the 1992 version introduced object orientation, and the 2000 version aligned SDL with some UML concepts such as the class diagram.

The main characteristics of SDL are: it is a graphical language, it is object oriented, it is event oriented, the model is independent from implementation, the language defines a strong semantic of execution and it contains abstract data types. Because it embeds abstract data types and a syntax to manipulate data, SDL models are formal (complete and non-ambiguous). An SDL model can be fully described because of this characteristic but it does not have to be. It is possible to describe non-deterministic models with, for example, the use of

the ANY keyword allowing to describe "any" input or "any" execution path. It is also possible to leave out some operations with the use of undefined "OPERATORS" describing an operation interface and leaving the implementation to the designers. An SDL model can also contain informal operations written in natural language. So depending on the level of precision within the model, an SDL system can be informal or very precise. SDL has built-in concepts and services such as processes, messages, timers, and procedures. All these concepts are supported by most RTOS making implementation on a real target straightforward.

The strong semantic of SDL and its built-in services describe an SDL virtual machine on which a model is based. This is actually the main characteristic of the platform-independent model. The definition of eventual external operators, and the implementation of the SDL services provided by the SDL virtual machine constitute the actual definition of the platform, the platform definition model. From the PIM and the PDM, it is possible to fully generate the platform-specific model in an executable language such as C code. As SDL became increasingly used in telecommunications systems, it appeared its built-in concepts were pretty close to the ones used in real-time operating systems:

• the system is decomposed into tasks running concurrently,

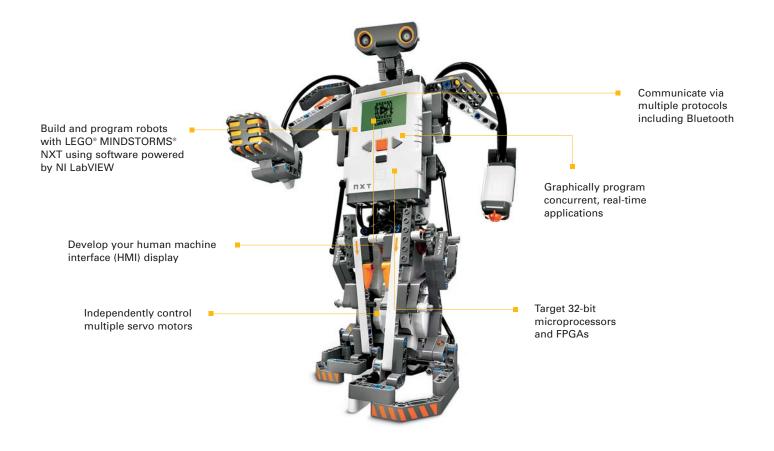

## NI LabVIEW.

## Limited Only by Your Imagination.

Real-Time and Embedded

Signal Processing

**High-Performance Test**

Industrial Control

### PRODUCT PLATFORM

LabVIEW Real-Time Module

LabVIEW FPGA Module

LabVIEW Embedded Development Module

NI CompactRIO Embedded Hardware Platform When the LEGO Group needed parallel programming and motor control tools intuitive enough for children, it selected graphical software powered by NI LabVIEW. With LabVIEW graphical system design, domain experts can quickly develop complex, embedded real-time systems with FPGAs, DSPs, and microprocessors.

>> Expand your imagination with technical resources at ni.com/imagine

Austria 0662 / 45 79 90 0 Belgium 02/757 00 20 Czech Republic 420 224 235 774 Denmark 45 45 76 26 00 Finland (09) 725 725 11 France 01 57 66 24 24 Germany 089 / 741 31 30 Hungary 36 23 501 580 Ireland 353 (0) 1867 4374 Israel 03 6393737 Italy 39 02 41309277 Netherlands (0348) 433466 Norway 47 (0) 66 90 76 60 Poland 48 22 3390 150 Portugal 351 210 311 210 Russia 7 495 783 6851 Slovenia/Croatia 386 3 425 4200 Spain (91) 640 0085 Swedden 08 587 895 00 Switzerland 056 / 200 51 51 LIK 01635 523545

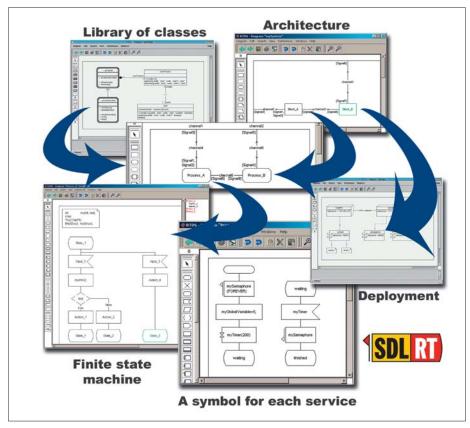

SDL-RT diagrams

- most of the tasks are based on extended finite state machines,

- tasks communicate with messages sent to message queues,

- built-in timers help to deal with unexpected behaviour.

Most telecommunications manufacturers have used SDL to design their software and some of them have measured the added value when using this modeling language. The results are impressive: it has increased quality by a ratio of 5 and reduced the overall development time by 35% in average.

In 1997, the object management group standardised the Unified Modelling Language, a merge of different object-oriented modelling approaches, most of them coming from the database application domain. The first versions of UML, versions 1.x, were too generic to support a platform-independent model. They did not contain any of the real-time operating system concepts such as task, semaphores, and timers. They did not contain any semantic, nor any data type. In order to use UML to describe a PIM, version 2 of UML introduced the concept of profiles to make UML more precise within each application domain. A profile allows to introduce specialized concepts and some semantic within a UML model. But the OMG did not define any standardised profile. Therefore UML 2 tools have introduced their own profiles, most of the time without documenting them, making the models tied to the tools they have been designed with, and tied to the underlying profile that was used. The ITU has taken this opportunity to work on a UML profile for telecommunications systems based on SDL under the Z.109 reference. The standard should be in force by the end of 2007, at that time SDL will be a standardised UML profile for telecommunications systems.

Because UML is very abstract and informal it is mostly used in the early phases of the development process when analysing and setting the requirements on the system. When it comes to coding, traditional textual languages are at the same level as the SDL abstract data types. Because of its graphical abstractions dedicated to telecommunication systems, SDL is positioned between the very generic UML and the very specialized coding languages.

When using SDL, telecommunications manufacturers found the concepts within the language were not exactly the ones available in the real-time operating systems nor the ones in textual languages. For example, in SDL messages have priorities and processes do not; on an RTOS it is the other way around, tasks have priorities but messages do not. As another example, in SDL it is possible to define arrays indexed on reals, which is very tricky to implement in C. To fully conform to SDL, code generators had to support all the SDL concepts and produced complex and

illegible code. So in order to be efficient, most of the telecommunications manufacturers broke the SDL semantic to use the one from their operating systems, and wrote C code manipulating C data types instead of the SDL data and syntax. They were actually already using what we call SDL-RT. As previously explained, SDL-RT comes from industrial practice and its first version has been written by PragmaDev so that everybody has a common way of combining UML, SDL, and C or C++. The specification is freely available on http://www.sdl-rt.otg, and is easy to read compared to an official standard. The storage format is XML so that the description is not tied to any tool. Since SDL-RT aims at all realtime and embedded applications, the semaphore concept has been introduced in the language so that each service of a real-time operating system has a dedicated graphical symbol. SDL-RT concepts are now proposed to ITU in order to be standardised. So eventually SDL-RT will most likely become a standardised UML profile for realtime applications.

### SDL-RT diagrams are:

- the class diagram in which passive classes are further described in C++ and active classes are further described using the SDL finite state machine,

- the architecture diagram which decomposes the system in hierarchical functional blocks down to the process level,

- the process behaviour which is described using the SDL finite state machine because it is much more detailed than ones from UML,

- the deployment diagram for distributed systems,

- the message sequence chart (MSC) to document execution scenarios similar to the UML sequence diagram.

Each service of the RTOS has a dedicated symbol: dynamic task creation or deletion, message input and output, timer start, cancel, and time out, semaphore takes or gives.. All views are related to each other making the model of the system consistent.

Since its inception twenty years ago, SDL has been a model-driven language for the specification of telecommunications systems. Following industrial practice, SDL-RT has extended the application domain to all applications based on real-time operating systems.. In the meantime, UML 1 being too generic, UML 2 has introduced the possibility to define profiles dedicated to an application domain but has not standardised any. Each UML 2 tool has therefore implemented a proprietary profile that is rarely documented making portability to another tool impossible. The ITU is standardising a UML profile for telecommunications systems based on SDL. The profile should be finalised by the end of 2007. ■

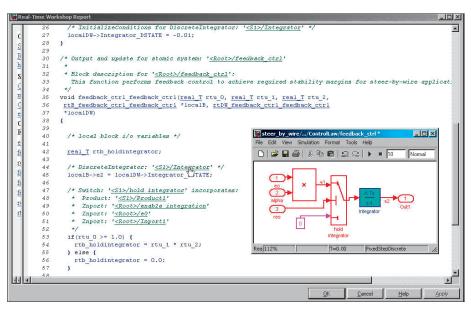

# Steer-by-wire system development with model-based design

### By Joachim Langenwalter and Tom Erkkinen, The MathWorks

Model-based design enables the automatic generation of final-build software from models for high-volume automotive embedded systems. A software engineering framework is needed to support this. This article presents a framework of processes, methods and tools for the design of automotive embedded systems.

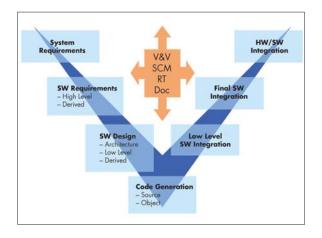

Figure 1. V diagram of the software process

■ Production code successes have recently been reported in various industries from companies including Denso, Motorola and Toyota. This technology is taking hold as an important component within the next evolution of software development. Although the impact on the software engineering process as a whole is understood, it has not been clearly established. This is especially apparent to participants of previous, similar evolutions including the migration from machine code to assembly code, and then to source code. With increased abstraction and automation came new processes, methods and tools.

However, due to difficulty of use, understanding or limited tool support, not every good idea has flourished. Evidence shows that these methods and tools are not always practical for mainstream production usage. For example, formal methods where proofs are used to ensure software correctness are written in a language that only a few experts worldwide truly understand. Further, real-time Case tools in the 1980s aided design, but did not provide an easy path to final code. Production code generation has done well in the early adoption stage, due mainly to its practicality. However, further growth requires integrated process, methods and tools to support it. A new process will be successful only with such methods and tools. If one of these pieces is missing, the effort to reengineer a company's mature embedded system is no longer feasible or practical. This article presents such a framework focused on production code generation:

- Process model-based design.

- Methods modelling, simulation, rapid prototyping, production code generation, model testing and coverage, and in-the-loop testing.

- Tools development tools, V&V tools, and integral tools.

Model-based design supports the needs of controls/DSP systems engineers and software developers by providing a common environment for graphical specification and analysis. In this process, models are made and used to specify system data, interfaces, feedback control logic, discrete/state logic, and real-time behaviour. Model-based design is used in nearly every industry that requires embedded control systems development. It is particularly well-entrenched in development processes for embedded applications such as large-scale automotive electronic control units. DSP and communications applications also use this approach, but emphasise modelling and prototyping rather than production code generation. To satisfy these various applications, the model-based design process must address the needs of safetycritical systems such as steer-by-wire systems. The process must also yield a final, executable code that is extremely compact, fast and traceable. This is due to the high volume nature of mass-produced ECUs, which necessitate the use of low-cost, fixed point microcontroller units and DSPs.

Model-based design fits within the context of any process framework, including those characterised in IEEE software engineering standards. IEEE Std. 730 applies to any general-purpose software project. A good understanding of its process framework results from a review of its stated requirements for critical project documentation.

Model-based design places great emphasis on process iterations, early testing, and reuse throughout the development process, making it both unique and powerful. The practicality inherent to this process is demonstrated at the bottom of the V: production code generation is an automatic transition from design. In model-based design, a block diagram or a state diagram model can serve as the system and software requirements, software design, or, with a slight change of perceptions, the source code. Also unique to this process is the extensive V&V effort that is made prior to a final build.

The benefit of early V&V is clear: fewer bugs will be found and less rework will be performed during final system integration and test. Catching a bug on the desktop is highly preferable to

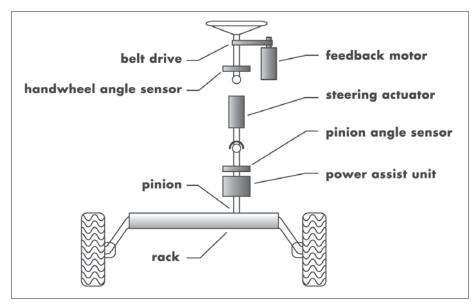

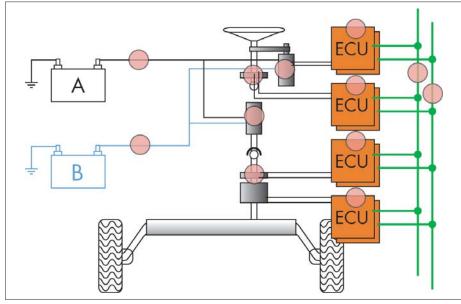

Figure 2. Steer-by-wire system

Figure 3. Possible faults on the steer-by-wire system

encountering it during a winter test drive in Finland. Organisations can leverage this benefit to achieve faster time to market.

Model-based design methods are employed during the software engineering process. A concise description of each development method is provided below, with examples and tool support information. Note that all the tools shown herein are commercially available. The following sections step through the development activity and include key V&V methods. Finally, the article concludes with the integral components.

Models are used for specifying requirements and design for all aspects of every individual subsystem (e.g. steer-by-wire). A typical system includes: inputs (e.g., steering wheel sensors), controller or DSP model, plant model (DC

motor, rack and pinion, wheels), outputs (change of direction). As shown, a system model can be created to represent the desired behaviour using control system block diagrams for feedback control, state machines for discrete events and conditional logic, and DSP blocks for filters. The model is then executed and analysed to ensure that the requirements are satisfied, using methods such as time- or event-based simulation and frequency domain analysis. For example, a steer-by-wire system must respond to a sensor failure and "shall attenuate high frequency response below 3db and not lag commanded rate by more than 1.5 m/sec".

Modelling and simulation of the steer-by-wire system in figure 2 determine if these requirements conflict or are valid. Simulation is a core validation activity and ensures that a system can

be realised to satisfy the requirements. Due to inaccurate plant models and insufficient processing power required to get a working solution on production silicon, modelling alone does not provide the total solution. To overcome these shortcomings, rapid prototyping is extremely useful because it replaces the plant model with the physical plant. In the steer-bywire example the plant might be a car, and in that case, an actual car is used. However, because the system is not yet built, a real-time or embedded platform runs the controller software and interacts with the plant.

There are two forms of rapid prototyping: functional and on-target. Functional prototyping uses a powerful real-time computer such as a multiprocessor floating point PowerPC or DSP system. The goal is to determine if the system controls the physical car as well as it controlled the modelled car. If so, the plant model inaccuracies are shown to be insignificant, and the control strategy is validated. On-target rapid prototyping executes the software in the same or similar production MCU or DSP, rather than a high-end PowerPC core or other dedicated high-end rapid prototyping hardware.